随着人工智能特别是大模型的飞速发展,对计算能力的需求呈指数级增长,推动了计算架构从单GPU节点向大规模异构集群的演进。在此背景下,系统性能瓶颈已从GPU内部计算转向多处理器间的数据交互效率,即“通信墙”问题。传统的互连技术难以满足现代AI工作负载对高带宽、低延迟的极致要求。为应对这些挑战,全向智感互联OISA(Omni-directional Intelligent Sensing Express Architecture)应运而生。OISA是一种旨在突破通信瓶颈的开放式GPU互连架构,其核心特点是原生支持共享内存语义,通过将通信操作抽象为GPU标准的内存读写和原子操作,并结合统一总线寻址(UBA)以及硬件与软件栈协同的地址转换与一致性维护机制,致力于简化并行编程,提高带宽效率并降低通信延迟。本文将深入剖析高效GPU间通信的必要性,阐述GPU的内存层次架构与通信语义基础,详细介绍OISA协议原生支持内存语义的核心要素,其支持先进的GPU内存管理抽象技术(如固定内存、统一虚拟寻址、按需页面迁移和设备自主内存管理)。最后,总结OISA的价值主张及其对未来高性能计算和AI硬件生态系统的潜在影响。

AI时代对先进GPU互连的迫切需求

AI工作负载的指数级增长与通信瓶颈

当前,人工智能工作负载,特别是大模型正驱动计算需求呈指数级增长。例如,GPT-4的参数规模据称达到1.8万亿,而Meta的Llama 3 405B模型在预训练阶段需要超过16000块NVIDIA H100 GPU和700TB的内存。这种巨大规模智算基础设施凸显出系统性能越来越多地受到GPU间数据交互效率的制约,而非原始计算能力本身。所谓的“通信墙”问题,即数据迁移与同步操作消耗大量执行周期的现象,在大模型训练与推理场景中尤为突出。以DeepSeek为代表的MoE模型由于其稀疏激活和数百个专家并行特性,进一步加剧了这一问题,产生了大量的AlltoAll通信模式,这对互连带宽和延迟提出了极为苛刻的要求,以保证梯度的有效交换和激活值的传递。

传统互连技术的局限性

传统的互连技术,尤其是PCI Express,虽然是系统连接的基石,但其架构(如SerDes速率限制、主从机制、协议开销等)在高密度、大规模GPU集群中逐渐显得力不从心,难以满足现代AI工作负载对带宽和延迟的极致需求。通信墙的多维度特性不仅体现在原始带宽不足,还包括预留字段不足、Lanes数量限制、不利于特定工作负载的拓扑结构,以及在处理如MoE模型中常见的复杂通信模式(如AlltoAll)时效率低下等问题。因此,行业亟需一种整体的、层次化的通信语义方法,而非孤立的点状优化。

超级节点的出现与新型互连的需求

为了支撑参数量达到万亿甚至更高的超大模型,计算架构正朝着“超节点”方向发展。超节点是指在单个机箱或紧密耦合的集群内部署大量GPU,形成一个强大的计算单元。这种架构对节点内部的GPU间互连技术提出了核心支撑需求。在此背景下,中国移动提出了全向智感互联OISA(Omni-directional Intelligent Sensing Express Architecture)开放架构,旨在解决超万亿参数模型训练中的通信瓶颈问题。

GPU间通信的架构基础

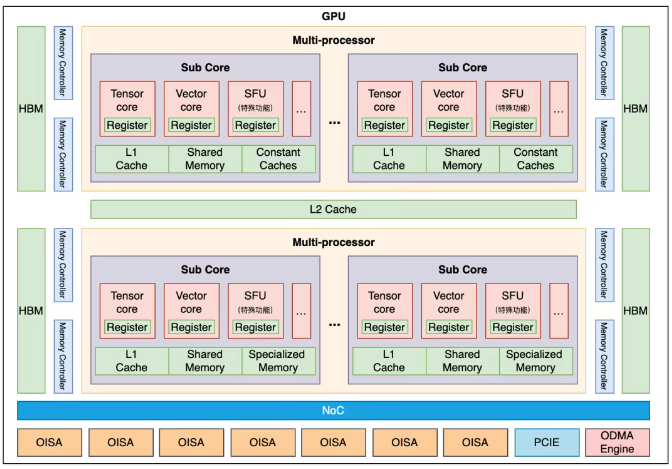

现代GPU架构:众核并行范式

现代GPU的核心采用众核(Many-Cores)设计,集成数以百计甚至上千个处理单元,每个单元内部包含大量算术逻辑运算核心(ALU)和专用加速模块,如矩阵计算、张量计算等。这种架构通过超大规模并行计算单元协同工作,使GPU芯片能够同时处理数以万计的运算线程。其执行模型通常基于单指令多线程(SIMT)模式,线程以固定数量的线程束为单位进行调度和管理,这些线程束在多处理器内部同步执行相同的指令序列,但每个线程处理不同的数据片段。编程模型方面,通常将运算任务组织成多层次的线程结构,通过这种划分方式来映射和利用GPU的海量计算资源。

图1:典型支持OISA协议的GPU架构图

GPU内存层次:性能与容量的权衡

GPU拥有复杂的内存层次结构,每一层级在容量、访问延迟和带宽特性上存在数量级的差异,深刻影响着通信机制的设计。

(1)寄存器堆(Registers): 寄存器是CPU或GPU核心中速度最快的存储单元,通常是每个硬件线程(hardware thread)都有自己独立的一套寄存器。这样可以避免线程间的寄存器访问冲突,并支持快速的上下文切换。寄存器位于处理器核心内部,可以直接被执行单元访问,通常在一个或几个时钟周期内完成访问,是内存层级中最快访问速度组件,通常在纳秒级别。寄存器总容量相对于缓存或主内存来说非常小,虽然具体的数量因架构而异,但每个线程分配到的寄存器空间通常在几十到几千字节的范围内,编译器会将线程当前正在使用或即将使用的数据尽量存储在寄存器中,以最大化计算速度。

(2)共享内存(Shared Memory):共享内存存在于每个流式多处理器的芯片上,对于内部执行的所有线程块及其包含的全部线程而言,这是一块共享的存储区域,使得流式多处理器内部的多个Cores均能访问同一份共享内存。其访问速度极高,远超全局内存,但通常略逊于寄存器。共享内存的容量相对有限,具体大小会依据不同的GPU架构而有所差异,一般从几十KB到一百多KB不等。它的生命周期与线程块的执行周期相绑定,即在线程块开始于流式多处理器上执行时分配,并在线程块执行完成后释放。与硬件自动管理的L1缓存不同,共享内存是由程序员进行显式管理和使用的一块高速片上内存,程序员需要负责将数据从全局内存加载至共享内存中进行操作,以此充分利用其高带宽和低延迟的特性,这对于线程块内部线程间需要频繁数据共享的计算场景尤其能带来显著的加速效果。

(3)一级缓存(L1 Cache):通常较小且速度快,是处理器(在如GPU的多并行处理器架构中,通常指流式多处理器)内部的硬件管理缓存,用于加速全局内存访问。其具体的共享机制会因处理器架构而异,有时是每个核心独享,有时在核心组内共享。共享内存是处理器内部一块由程序员显式管理的高速片上内存(或称作暂存器),不属于硬件自动管理的缓存。它用于在同一线程块内的线程之间进行高速数据交换和数据复用。共享内存的访问延迟远低于全局内存。

(4)二级缓存(L2 Cache): 在大多数现代GPU架构中,L2缓存是一个统一的、由所有流式多处理器共享的资源,这与处理器内部核心组之间的L1缓存共享不同。在缓存层级中,L2缓存的容量总是大于L1缓存,以提供更大的缓存空间来捕获更多的数据重用。L2缓存的主要作用就是缓存来自全局内存(显存)的数据。通过缓存命中(cache hit),可以避免访问延迟高得多的主显存,从而显著提高内存访问效率和整体性能。

(5)专用只读内存(Specialized Read-Only Memory): 常量内存(Constant Memory)和纹理内存(Texture Memory)是GPU中设计为只读的专用内存空间。虽然底层数据可能存储在全局内存中,但从计算核心访问时是只读的,并通过专用的硬件路径和缓存进行优化。常量内存主要针对广播访问的优化,即同一线程束中的所有线程访问同一个内存地址的情况。在这种模式下,访问效率非常高。纹理内存主要针对二维或三维空间局部性访问优化,这在传统图形处理中非常常见,纹理硬件还提供了过滤和寻址模式等功能。这些硬件缓存针对各自的访问模式进行了优化,能够显著提高访问效率,减少对全局内存的访问。

(6)全局设备内存(Global/Device Memory - HBM/GDDR): 全局设备内存(显存)是GPU上容量最大的存储区域,现代GPU的显存容量可以达到上百GB甚至更高。为了满足模型装载需求,全局内存通常采用HBM等高带宽技术,提供非常高的内存带宽,可以达到TB/s级别。相对于寄存器、共享内存和L1/L2缓存,全局内存的访问延迟最高,通常在数百纳秒。这是因为数据需要通过显存控制器和内存总线从显存芯片中读取。全局内存是GPU与Host(CPU)之间以及多GPU之间进行数据传输和交换的主要场所。由于其高延迟原因,对全局内存的访问模式(如合并访问)是GPU编程的关键优化点。跨GPU卡间通信通常通过专用互连架构,将源GPU计算任务产生的数据直接传输至目标GPU的内存地址空间,实现多处理器间的显存数据读写。GPU的内存层级(寄存器、L1 Cache、L2 Cache、专用制度内存、全局内存)具有不同的数据一致性(coherence)和内存一致性(consistency)模型。由于存在缓存以及并行访问,为了确保多个线程(尤其是跨线程块的线程)对同一数据的访问顺序和可见性符合预期,程序员需要使用适当的同步机制(如内存屏障、原子操作)来维护数据一致性。

CPU与GPU:迥异的设计哲学与内存体系

CPU与GPU在架构设计理念上存在显著差异。CPU追求的是尽可能快地完成单个或少量复杂的任务,因此投入了大量晶体管用于复杂的控制逻辑(如深度流水线、分支预测、乱序执行),以提高指令级并行性和降低延迟。CPU也拥有层次深、容量大的缓存系统来减少内存访问延迟,并配备强大的SIMD单元来加速向量化计算。GPU的设计目标是为了处理大量相似数据的并行计算任务,因此将大部分芯片面积用于构建大量的计算单元(ALUs)。

为了支持海量线程的并行,GPU简化了单个线程的控制逻辑,采用更适合并行执行的架构(如SIMT - 单指令多线程),并通过隐藏内存访问延迟来优先提高整体吞吐量。不同的设计目标导致了CPU和GPU在内存层次结构、缓存设计、数据访问模式以及编程模型上的差异,从而影响了程序员进行内存管理和CPU与GPU之间交互的复杂度。在多GPU系统中,GPU之间需要频繁交换数据。如果互连技术的带宽不足或延迟太高,就会成为瓶颈,限制整个系统的并行效率和吞吐量。高带宽、低延迟的OISA互连技术对于构建高性能多GPU系统至关重要。

弥合CPU-GPU鸿沟:异构内存挑战

在典型的异构计算系统中,CPU内存与GPU内存物理上相互隔离,它们之间通过诸如PCIe等高速总线进行数据传输。然而,这种通道的带宽和延迟远不及GPU访问其本地内存的效率。因此,优秀的系统设计需要尽量减少CPU与GPU间的数据搬运次数,并采用固定内存(Pinned Memory)分配技术,将主机内存页面锁定,避免操作系统分页操作干扰,从而实现CPU与GPU内存之间更高效的批量数据传输。同时,利用异步传输等技术手段来隐藏或缩短传输耗时。

针对异构计算系统中CPU与GPU内存物理隔离的挑战,业界致力于打通异构内存访问机制,OISA正在探索通过统一内存地址(UMA)技术,它提供了一个统一的虚拟地址空间,允许GPU通过指针访问主机内存。这种设计将简化编程模型,并在一定程度上使得主机内存可以作为GPU内存的扩展,将GPU可用的有效内存容量大幅提升,而GPU内存容量是影响大型模型参数量的一个关键指标。但这也会带来通过互连总线访问远端内存的效率损失,如何在性能和容量之间做取舍和平衡,需要依赖具体的业务特性进行适配。