通信世界网消息(CWW)即使芯片架构自研、IP核国产化,离开Synopsys等企业的EDA工具,设计仍可能沦为无法流片的代码。这一隐忧在5月23日美国商务部工业与安全局(BIS)的一纸禁令后变得更为现实——BIS通知EDA巨头Synopsys、Cadence、Siemens EDA,要求其停止向中国提供技术。

禁令一出,市场应声而动:被点名的美国EDA企业股价普遍跌超10%,而国产EDA企业华大九天、概伦电子则分别大涨15%与20%。为深度剖析此次禁令对产业的影响力及应对策略,工信智媒体(通信世界)记者采访了隼瞻科技创始人兼CEO曾轶,聆听来自产业界最前线的声音。

驭势:中长期的“危”与“机”

EDA软件作为集成电路领域的上游基础工具,贯穿设计、制造、封测全流程,是提高芯片设计效率的核心支撑。该领域工具种类繁多、分工精细、技术壁垒高。目前,全球仅有Synopsys、Cadence和Siemens EDA三家企业能提供从前端到后端的全流程解决方案。尽管国内EDA企业已在特定领域及部分点工具上实现了技术突破,但仍无法独立提供全流程EDA工具。

据Mordor Intelligence数据,2024年全球EDA市场规模已达186亿美元,而同期中国EDA市场规模19.2亿美元,约占全球EDA市场的10.3%。“EDA和光刻机一样都是我国集成电路产业发展的核心‘短板’,美国封禁EDA软件,无异于掐住了我国集成电路行业的‘七寸’。”曾轶讲道。

短期来看,此次事件的冲击显著且严峻。Synopsys、Cadence、Siemens EDA在国内市场占据近90%的份额,其断供将直接威胁部分国内先进制程(特别是7nm及以下)芯片设计项目,可能导致工具链中断、更新停滞、技术支持缺失,进而引发项目延期甚至搁浅。高度依赖国际EDA工具进行复杂SoC设计、先进封装、良率分析等环节的头部设计公司和晶圆厂,亟需寻找替代方案或调整技术路线。

长期而言,此次断供将从根本上重塑中国半导体产业的认知和发展路径,强力驱动EDA国产化替代进程,推动设计、制造、封测、IP、工具全产业链强化协同,共同构建自主可控的产业生态。“某种程度来说,这是倒逼中国EDA产业实现跨越式发展的‘催化剂’,但过程必然伴随阵痛和挑战。”

在曾轶看来,此次事件充分证明了EDA作为半导体产业基石的不可替代性。这既是一场危机,更是前所未有的机遇。它彻底打破了产业链对“全球化供应链绝对可靠”的幻想,凝聚了“自主可控是唯一出路”的共识。“我们视此为国产EDA产业发展的关键转折点,责任重大,但信心倍增。”

攻坚:国产替代尚存多重瓶颈

事实上,在国产芯片行业快速发展的背景下,我国EDA产业整体步入快速成长期,正加速从“点工具突破”向“全流程覆盖”和“先进工艺支持”迈进。部分国产EDA企业在数字前端验证、部分模拟设计、封装分析等特定领域已建立较强竞争力,能够满足中端工艺节点的芯片设计需求。然而,在EDA整体生态的完整性、工具链的协同性、对先进工艺的深度支持以及IP库的丰富度方面,与三巨头仍存在显著差距。

“中国是全球最有潜力的大市场,这里孕育了全球最大的互联网市场,培育了一批出色的智能汽车企业,EDA产业只是需要时间和机会。”曾轶表示。过去五年间,国内芯片EDA企业数量已经从10家增长到120家以上;预计到2025年,国内本土EDA市场年均复合增速将超过14%,远高于全球市场。

曾轶认为,未来国产EDA工具发展将经历三个阶段:短期内,与工艺节点解耦的国产EDA工具将迎来发展良机,可通过深化客户协作,快速入迭代产品,抢占市场份额;未来3年内,通过集中攻关和生态协同,有望实现核心EDA工具的“基本可用”——即覆盖主流成熟工艺,满足大部分设计需求;长期要实现“好用”与“全而强”——即全面支持最先进工艺,在性能、精度、易用性上比肩国际巨头,并构建起强大的生态。

而要实现目标,加速国产EDA发展,业界还需正视并突破当前的主要瓶颈:核心算法、先进工艺支持、全流程整合等技术瓶颈;用户切换惯性、国产IP匮乏与晶圆厂协同不足等生态瓶颈;顶尖算法、架构工程师稀缺等人才瓶颈;先进工艺项目实战机会短缺等市场验证瓶颈;研发周期长、投入大等发展瓶颈。

曾轶指出,解决之道在于生态共建与技术聚焦,单打独斗难以成功,唯有产业链各方形成合力,共同定义需求、协同开发、共享成果,通过国内厂商结合自身优势,选择关键突破口,实现差异化竞争,方能加速破局。作为一家专注于RISC-V专用处理器IP和EDA设计平台的创新型高科技企业,隼瞻科技正积极参与并推动产业发展。

思变:隼瞻科技打造两大王牌

“EDA断供的短期阵痛集中于7nm以下先进制程设计,但更深层的挑战在于处理器设计权的缺失。”曾轶指出,当前中国半导体产业面临双重困境:一方面,传统EDA工具断供卡住了芯片设计的“咽喉”;另一方面,ARM等处理器IP授权体系仍制约着芯片架构的自主性。

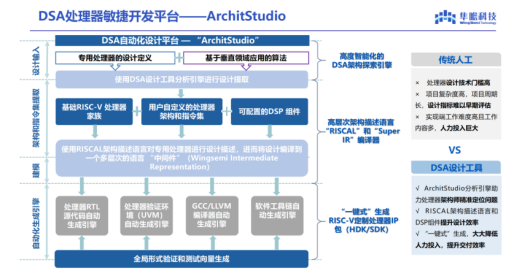

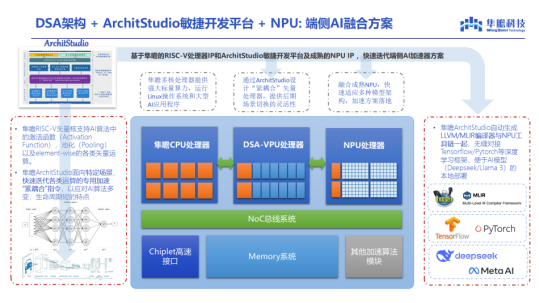

面对上述挑战,隼瞻科技打造了自主可控的RISC-V专用处理器解决方案和配套架构设计EDA产品——DSA处理器敏捷开发平台ArchitStudio,并推出多种模式结合的IP定制开发解决方案,产品涵盖高中低端专用处理器门类,可广泛应用于AIOT、DSP、5G网络、汽车电子、人工智能、高算力运算等多种复杂芯片解决方案。

其中,ArchitStudio对标Synopsys、Cadence、Codasip等国外知名企业的相应产品,并在部分技术层面展现出显著优势,大幅降低了RISC-V处理器设计的门槛,为基于RISC-V定制处理器的SOC设计方法学带来了革命性的改变。借助ArchitStudio,设计人员得以摆脱RTL和编译器级别的繁复开发工作,更专注于架构和指令集的设计;快速生成RTL代码和SDK工具链,形成处理器架构设计和性能评估的敏捷迭代,大幅度提升RISC-V处理器的设计效率,显著降低人力投入成本。

同时,ArchitStudio具备超高的AI素养。在曾轶看来,EDA行业是一个天然的AI容器,所有EDA工具都值得用大模型重做一遍。隼瞻科技和国内先进大模型公司进行合作,在ArchitStudio内置了多种人工智能专用模型,能通过分析推导不断测试和优化设计方案,提升处理器的各项关键指标。在某AI芯片企业的案例中,工程师输入特定AI应用的算法特征,平台通过强化学习自动生成匹配的向量处理器架构,使芯片能效比提升300%,而传统方法需要18个月的设计周期被压缩至22周。

总体来看,依托隼瞻科技的RISC-V处理器IP家族为“基胚”,结合客户垂直领域特定算法,并辅以高效的ArchitStudio平台化设计,用户可高效定制出符合特定应用需求的DSA处理器,形成强大的垂类产品竞争力。例如,基于ArchitStudio开发的AI处理器方案,其算力覆盖范围广泛:0.1 T~1T低算力区间主要面向消费电子及物联网(IoT)市场;1 T~5T区间可满足通信设备、工业控制及服务机器人等需求;而5 T~ 50 T的高算力区间,则能覆盖AI一体机和AI算力服务器等市场领域。目前,隼瞻科技已经与科研院所、运营商、设备商建立深度合作。

破局:聚焦五大主线突出重围

“我对未来3—5年我国EDA产业实现关键突破并支撑半导体自主可控抱有充分的信心。”曾轶指出,这份信心源于国家层面对EDA工具前所未有的战略重视与资源投入;国际环境倒逼与国内芯片产业蓬勃发展创造的巨大刚需和市场空间;设计、制造、EDA、IP等全产业链协同意愿的空前增强;国内厂商的技术积累与海外高端人才回流趋势;AI/云等新技术带来的“换道超车”机遇。

当然,前路依然艰辛,产业要清醒认识到技术差距的深度、生态建设的长期性以及国际环境的复杂性,聚焦以下几方面实现关键突破。

一是全流程整合与协同,打破工具“孤岛”,实现国产工具链无缝集成与数据互通,提升整体设计效率。

二是先进工艺节点攻坚,集中力量突破7nm及以下工艺的EDA支持,尤其是物理签核和制造接口,深化与本土晶圆厂的PDK联合开发。

三是AI与EDA深度融合,将AI从辅助升级为核心驱动,在布局布线、验证、功耗、良率等环节实现革命性突破。

四是构建强大健康生态,重点发展高质量国产IP库,尤其是接口和基础库IP;建立完善国产EDA工具间标准接口;通过政府引导、标杆示范、联合实验室等方式,鼓励设计公司采用国产工具。

五是夯实基础与人才根基,持续投入EDA底层核心算法研究;建立长效的高端EDA人才培养与引进机制。

挑战虽巨,机遇更大。曾轶表示,隼瞻科技愿与国内同仁一道,以开放的心态、坚定的信念、持续的创新,共同推动中国EDA产业突破重围,为中国半导体产业的自主可控贡献坚实力量。